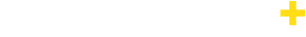

Microchip vừa công bố giải pháp ở lớp vật lý nhỏ gọn nhất trong ngành, có mức tiêu thụ điện năng thấp và thông lượng 1,6T (terabits trên giây), được trang bị chip PM6200 META-DX2L của công ty với khả năng hạ thấp 35% mức tiêu thụ điện năng trên mỗi cổng so với sản phẩm tiền nhiệm là PAM4, META-DX 156G – giải pháp lớp vật lý ở cấp độ terabit đầu tiên trong ngành.

Các thiết bị định tuyến, thiết bị chuyển mạch và card đường dây luôn đòi hỏi băng thông, mật độ cổng lớn hơn cùng kết nối Gigabit Ethernet tới 800 Gigabit để hỗ trợ được lưu lượng trung tâm dữ liệu ngày càng lớn do các dịch vụ 5G, điện toán đám mây, trí tuệ nhân tạo và máy học tạo ra. Để cung cấp băng thông lớn hơn, những thiết kế này cần phải vượt qua những thách thức trong đảm bảo tính toàn vẹn của tín hiệu phát sinh trong quá trình chuyển đổi sang kết nối PAM4 Nối tiếp/Song song (Serializer/Deserializer – SerDes) 112G (gigabits trên giây) cần thiết để hỗ trợ những máy thu phát quang, backplane hệ thống và bộ xử lý gói tin mới. Giờ đây, chúng ta có thể vượt qua những thách thức này bằng giải pháp ở lớp vật lý nhỏ gọn nhất trong ngành, có mức tiêu thụ điện năng thấp và thông lượng 1.6T (terabits trên giây) từ Microchip Technology Inc. (Nasdaq: MCHP) được trang bị chip PM6200 META-DX2L của công ty với khả năng hạ thấp 35% mức tiêu thụ điện năng trên mỗi cổng so với sản phẩm tiền nhiệm là PAM4, META-DX 156G – giải pháp lớp vật lý ở cấp độ terabit đầu tiên trong ngành.

Với băng thông 1.6T mật độ cao, kích thước nhỏ gọn giúp tiết kiệm diện tích, công nghệ 112G PAM4 SerDes và khả năng hỗ trợ các tốc độ Ethernet từ 1 đến 800 GbE, giải pháp META-DX2L Ethernet PHY của Microchip là một thiết bị có thể hoạt động ở điều kiện nhiệt độ trong môi trường công nghiệp với khả năng cung cấp kết nối đa dạng để tối đa hóa khả năng tái sử dụng thiết kế trên các ứng dụng, bao gồm từ thiết bị định thời, hộp số tiến hoặc hộp số lùi cho tới một bộ ghép kênh 2:1 không xảy ra hiện tượng mất gói tin. Các tính năng của hộp số và thiết bị đấu chéo có khả năng cấu hình cao khai thác tối đa băng thông I/O của thiết bị để hỗ trợ các kết nối linh hoạt cần thiết trên card đường dây đa tốc độ để hỗ trợ nhiều máy thu phát quang khác nhau. Các thiết bị PAM4 SerDes ở lớp vật lý với mức tiêu thụ điện năng thấp hỗ trợ tốc độ giao diện cơ sở hạ tầng thế hệ mới dành cho các trung tâm dữ liệu đám mây, các ứng dụng AI/ML, 5G và cơ sở hạ tầng của nhà cung cấp dịch vụ viễn thông cho dù đó là trên mạng cáp đồng kết nối trực tiếp trên khoảng cách lớn, trên backplane hay các kết nối với máy thu phát quang.

Microchip cung cấp tập hợp đầy đủ các thiết kế, tài liệu tham chiếu và bảng mạch dùng thử để hỗ trợ những khách hàng đang phát triển hệ thống bằng các thiết bị META-DX2L. Ngoài công nghệ ở lớp vật lý của mạng Ethernet, Microchip còn cung cấp cho các nhà phát triển giải pháp hệ thống một giải pháp hệ thống tổng thể trong đó bao gồm cả PolarFire® FPGA, PLL hiệu năng cao ZL30632, các bộ dao động, điều áp cũng như nhiều linh kiện khác đã được thẩm định từ trước bằng giải pháp hệ thống tổng thể META-DX2L, giúp đẩy nhanh tốc độ của quá trình từ khâu thiết kế đến sản xuất một cách nhanh chóng hơn.